Notes for Computer Architecture A Quantitative Approach Sixth Edition

Navigating

- Basic concepts : Chapter 1, Appendix A.

- Memory Hierarchy: Appendix B, Chapter 2, and Appendices D and M.

- Instruction-Level Parallelism: Appendix C, Chapter 3, and Appendix H.

- Data-Level Parallelism: Chapters 4, 6, and 7, Appendix G.

- Thread-Level Parallelism: Chapter 5, Appendices F and I.

- Request-Level Parallelism: Chapter 6.

- ISA: Appendices A and K.

- Appendix E.

Appendix E can be read at any time, but it might work better if read after the ISA and cache sequences. Appendix J can be read whenever arithmetic moves you. You should read the corresponding portion of Appendix M after you complete each chapter.

Part I: Basic Concepts

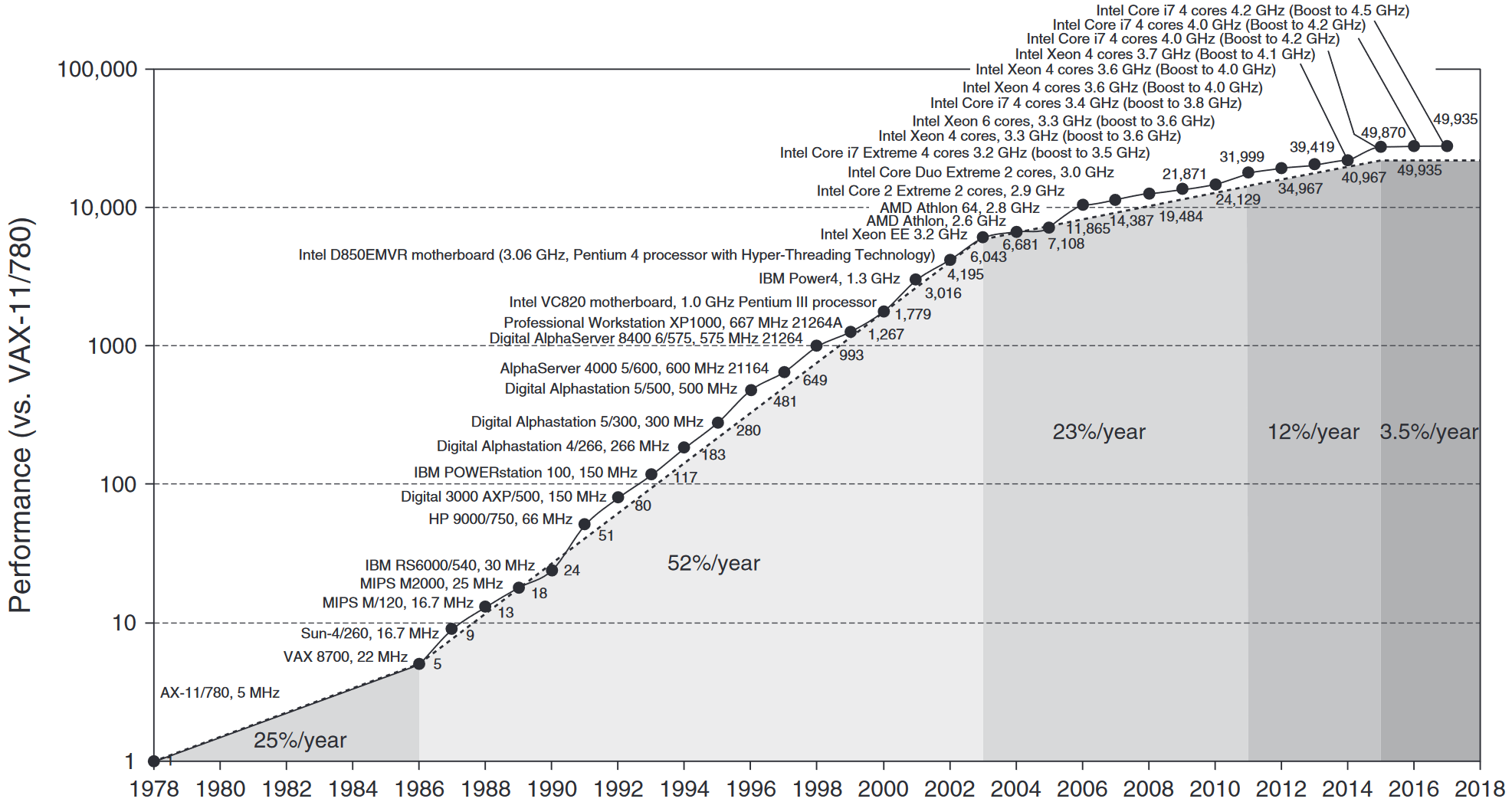

1.1 Chapter 1 Fundamentals of Quantitative Design and Analysis

Amdahl’s Law prescribes practical limits to the number of useful cores per chip.

Classes of Computers

- IoTs/Embeded Computers

- Personal mobile device (PMD)

- Desktop

- Server

- Clusters/Warehouse scale computers (WSC)

Classes of parallelism and parallel architectures

- Data-Level Parallelism (DLP)

- Instruction-Level Parallelism (ILP)

- Thread-Level Parallelism (TLP)

- Request-Level Parallelism (RLP)

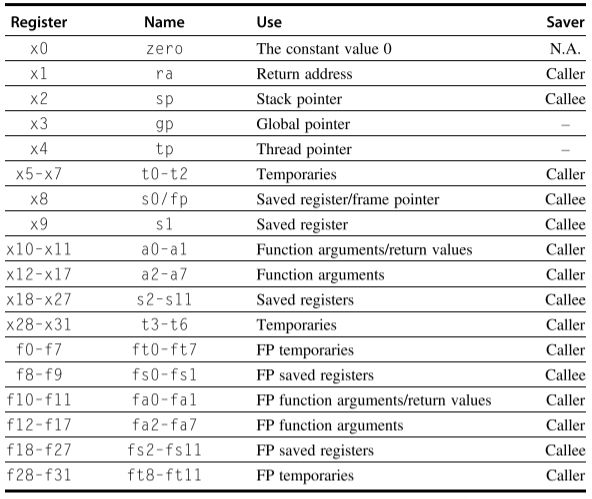

RISC-V registers, names, usage, and calling conventions.

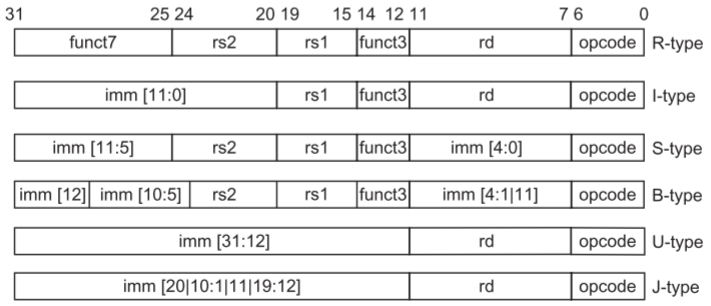

The base RISC-V instruction set architecture formats.

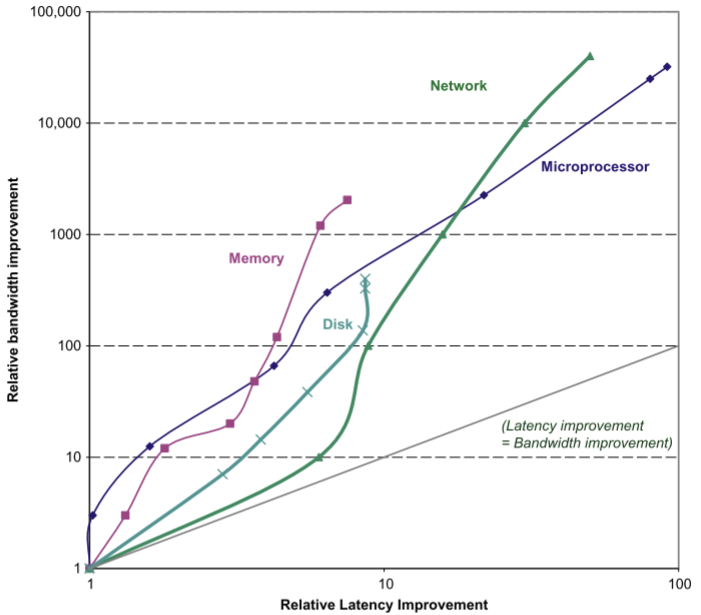

Bandwidth grows by at least the square of the improvement in latency.

The energy consumption required per transistor:

The power rqquied per transistor:

Modern microprocessors offer many techs to try to improve energy efficiency:

- Do nothing well.

- Dynamic voltage-frequency scaling (DVFS).

- Design for the typical case.

- Overclocking

Static power of a CMOS:

The only hope to stop leakage is to turn off power to the chips’ subsets.

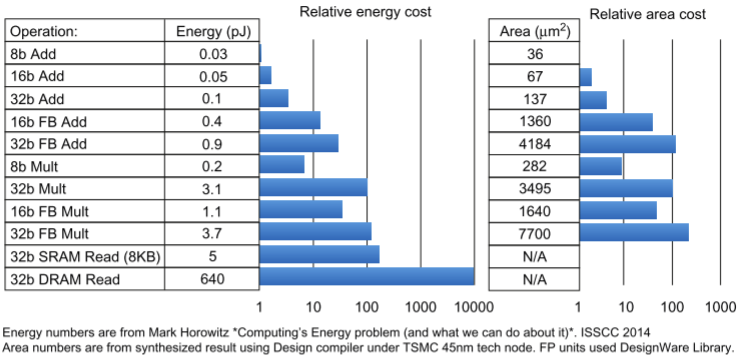

Comparson of the energy and die area of arithmetic operations and energy cost of accesses to SRAM and DRAM.

Cost of an integrated circuit:

Bose-Einstein formula (Calcuting the die yield):

There are two main measures for dependability

- Module reliability: mean time to failure (MTTF), falures in time (FIT), mean time to repair (MTTR).

- Module availabillity

Computing SPECRation arithmetically:

CPU time for a program:

1.2 Appendix A Instruction Set Principles

Classifying ISA:Stack, Accumulator, Register-memory, and Register-register/load-store.

Little Endian

Big Endian

Memory addressing mode: displacement, immediate, and register indirect.